# PATENT ABSTRACTS OF JAPAN

(11)Publication number:

06-311479

(43) Date of publication of application: 04.11.1994

(51)Int.Cl.

H04N 5/92

H04N 7/13

(21)Application number: 05-096094

(71)Applicant: HITACHI LTD

(22)Date of filing:

**22.04.1993** (72)In

(72)Inventor: HATANAKA YUJI

OKAMOTO HIROO

**NAKAMURA MASAFUMI**

SAITO SEIICHI

# (54) DIGITAL SIGNAL RECORDING SYSTEM, DIGITAL SIGNAL REPRODUCING SYSTEM AND DIGITAL SIGNAL RECORDING AND REPRODUCING SYSTEM

#### (57)Abstract:

PURPOSE: To provide a system capable of performing recording and reproduction neither too much nor too little by synchronizing compression picture signals composed of two kinds of digital signals not in a complete synchronization relation including jitters and to reduce the number of the connection signals of a receiver and a recording and reproducing device.

CONSTITUTION: The receiver 4 is provided with an output means 6 for bit— serially outputting received and demodulated first signals and second signals provided with intra—frames and the recording and reproducing device is provided with a first input means for inputting the first signals 32, a first storage means for storing the first signals inputted by the first input means, a second input means for inputting the second signals 35, a second storage means for storing the second signals inputted by the second input means and a recording means 14 for reading first storage signals stored in the first storage means and second storage signals stored in the second storage means at a same speed time base compressed from the time of input and recording them on a recording medium 18.

(19)日本国特許庁(JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号

# 特開平6-311479

(43)公開日 平成6年(1994)11月4日

(51)Int.Cl.5

識別記号

庁内整理番号

FΙ

技術表示箇所

H 0 4 N 5/92

H 4227-5C

7/13

Z

審査請求 未請求 請求項の数16 OL (全 20 頁)

(21)出願番号

(22)出願日

特願平5-96094

平成5年(1993)4月22日

(71)出願人 000005108

株式会社日立製作所

東京都千代田区神田駿河台四丁目6番地

(72)発明者 畑中 裕治

神奈川県横浜市戸塚区吉田町292番地 株

式会社日立製作所映像メディア研究所内

(72)発明者 岡本 宏夫

神奈川県横浜市戸塚区吉田町292番地 株

式会社日立製作所映像メディア研究所内

(72)発明者 中村 雅文

神奈川県横浜市戸塚区吉田町292番地 株

式会社日立製作所映像メディア研究所内

(74)代理人 弁理士 武 顕次郎

最終頁に続く

(54) 【発明の名称 】 ディジタル信号記録システム及びディジタル信号再生システム及びディジタル信号記録再生システム

### (57)【要約】

【目的】 ジッターを含み、完全な同期関係には無い2種類のディジタル信号からなる圧縮画像信号の同期化を行い、過不足無く記録再生できるシステムを提供すること。また、受信装置と記録再生装置の接続信号数を減少させること。

【構成】 受信装置4に、受信及び復調されたイントラフレームを含む第1の信号と第2の信号をビットシリアルで出力する出力手段6を設け、記録再生装置5に、第1の信号32を入力する第1の入力手段と、第1の入力手段で入力した第1の信号を記憶する第1の記憶手段と、第2の信号35を入力する第2の入力手段と、第2の入力手段で入力した第2の信号を記憶する第2の記憶手段と、第1の記憶手段に記憶された第1の記憶信号と第2の記憶手段に記憶された第2の記憶信号を、入力時より時間軸圧縮した同一の速度で読み出して記録媒体18上に記録する記録手段14を設ける。

#### 【特許請求の範囲】

【請求項1】 第1の信号と第2の信号からなるディジタル映像信号を受信及び復調する受信装置と、前記受信装置で受信した前記第1の信号と前記第2の信号を記録する記録装置とからなるディジタル信号記録システムであって、

前記受信装置で受信及び復調された前記第1の信号を入力する第1の入力手段と、前記受信装置で受信及び復調された前記第2の信号を入力する第2の入力手段と、前記第1の入力手段で入力した前記第1の信号と前記第2の入力手段で入力した前記第2の信号との同期化を行う同期化手段と、前記同期化手段により同期化された前記第1の信号及び前記第2の信号を記録媒体上に記録する記録手段と、を設けたことを特徴とするディジタル信号記録システム。

#### 【請求項2】 請求項1記載において、

前記第1の入力手段で入力した前記第1の信号を記憶する第1の記憶手段と、前記第2の入力手段で入力した前記第2の信号を記憶する第2の記憶手段とを設け、前記同期化手段は、前記第1の記憶手段に記憶された第1の記憶信号及び前記第2の記憶手段に記憶された第2の記憶信号を同期化された速度で読み出すことにより、前記第1の信号と前記第2の信号との同期化を行うことを特徴とするディジタル信号記録システム。

#### 【請求項3】 請求項1記載において、

前記第1の入力手段で入力した前記第1の信号を一時蓄える第1のバッファ手段と、前記第1のバッファ手段の出力信号を記憶する第1の記憶手段と、前記第2の入力手段で入力した前記第2の信号を一時蓄える第2のバッファ手段と、前記第2のバッファ手段の出力信号を記憶する第2の記憶手段とを設け、前記同期化手段は、前記第1のバッファ手段及び前記第2のバッファ手段を同期化された速度で読み出すことにより、前記第1の信号と前記第2の信号との同期化を行うことを特徴とするディジタル信号記録システム。

#### 【請求項4】 請求項1記載において、

前記第1の入力手段で入力した前記第1の信号または前記第2の入力手段で入力した前記第2の信号のどちらかを一時蓄えるバッファ手段と、前記バッファ手段の出力信号を記憶する記憶手段とを設け、前記同期化手段は、前記第2の信号または前記第1の信号と同期化された速度で前記バッファ手段を読み出すことにより、前記第1の信号と前記第2の信号との同期化を行うことを特徴とするディジタル信号記録システム。

【請求項5】 請求項1乃至4の何れか1つに記載において

前記第1の信号及び前記第2の信号はパケットを構成しており、前記受信装置には、前記第1の信号のパケットの周期を示す第1の同期信号と前記第2の信号のパケットの周期を示す第2の同期信号とを出力する手段を設

け、前記記録装置には、前記第1の同期信号を入力して 第1のパケット先頭信号を検出する第1の同期検出手段 と、前記第2の同期信号を入力して第2のパケット先頭 信号を検出する第2の同期検出手段とを設け、前記同期 化手段は、前記第1のパケット先頭信号の入力タイミン グに最も近いタイミングで検出された第2のパケット先 頭信号の記録タイミングを、前記第1のパケット先頭信 号の記録タイミングと同期化することを特徴とするディ ジタル信号記録システム。

【請求項6】 請求項1乃至5の何れか1つに記載において、

前記ディジタル映像信号は、全画面情報によって構成された信号と、前または後のフレーム信号との差分情報によって構成された信号とからなり、前記第1の信号は、前記全画面情報によって構成された信号を含むことを特徴とするディジタル信号記録システム。

【請求項7】 第1の信号と第2の信号からなるディジタル映像信号を再生するディジタル信号再生システムであって、

前記第1の信号と前記第2の信号を再生する再生手段 と、前記再生手段で再生された再生信号から前記第1の 信号と前記第2の信号を分離する分離手段と、前記分離 手段で分離された前記第1の信号と前記第1の信号に同 期した第1のクロックを出力する第1の出力手段と、前 記分離手段で分離された前記第2の信号と前記第2の信 号に同期した第2のクロックを出力する第2の出力手段 と、を設けたことを特徴とするディジタル信号再生システム。

#### 【請求項8】 請求項7記載において、

前記第1の信号及び前記第2の信号はパケットを構成しており、前記第1の信号のパケットの周期を示す第1の同期信号を前記第1の信号に同期して出力する第1の同期出力手段と、前記第2の信号のパケットの周期を示す第2の同期信号を前記第2の信号に同期して出力する第2の同期出力手段とを設けたことを特徴とするディジタル信号再生システム。

【請求項9】 請求項7または8記載において、

前記ディジタル映像信号は、全画面情報によって構成された信号と、前または後のフレーム信号との差分情報によって構成された信号とからなり、前記第1の信号は、前記全画面情報によって構成された信号を含むことを特徴とするディジタル信号再生システム。

【請求項10】 第1の信号と第2の信号からなるディジタル映像信号を受信及び復調する受信装置と、前記受信装置で受信した前記第1の信号と前記第2の信号を記録再生する記録再生装置とからなるディジタル信号記録再生システムであって、

前記受信装置で受信及び復調された前記第1の信号を入力する第1の入力手段と、前記受信装置で受信及び復調された前記第2の信号を入力する第2の入力手段と、前

記第1の入力手段で入力した前記第1の信号と前記第2の入力手段で入力した前記第2の信号との同期化を行う同期化手段と、前記同期化手段により同期化された前記第1の信号及び前記第2の信号を記録媒体上に記録された前記第1の信号と前記第2の信号を再生する再生手段と、前記再生手段で再生された再生信号から前記第1の信号と前記第2の信号を分離する分離手段と、前記分離手段で分離された前記第1の信号と前記第1の信号に同期した第1のクロックを出力する第1の出力手段と、前記分離手段で分離された前記第2の信号と前記第2の信号に同期した第2のクロックを出力する第2の出力手段と、を設けたことを特徴とするディジタル信号記録再生システム。

【請求項11】 請求項10記載において、

前記第1の信号及び前記第2の信号はパケットを構成し ており、前記受信装置には、前記第1の信号のパケット の周期を示す第1の同期信号と前記第2の信号のパケッ トの周期を示す第2の同期信号を出力する手段を設け、 前記記録再生装置には、前記第1の同期信号を入力して 第1のパケット先頭信号を検出する第1の同期検出手段 と、前記第2の同期信号を入力して第2のパケット先頭 信号を検出する第2の同期検出手段と、前記再生手段に より前記記録媒体より再生された前記第1の信号に同期 した第3の同期信号を出力する第1の同期出力手段と、 前記記録媒体より再生された前記第2の信号に同期した 第4の同期信号を出力する第2の同期出力手段とを設 け、前記同期化手段は、前記第1のパケット先頭信号の 入力タイミングに最も近いタイミングで検出された第2 のパケット先頭信号の記録タイミングを、前記第1のパ ケット先頭信号の記録タイミングと同期化することを特 徴とするディジタル信号記録再生システム。

【請求項12】 請求項10または11記載において、前記ディジタル映像信号は、全画面情報によって構成された信号と、前または後のフレーム信号との差分情報によって構成された信号とからなり、前記第1の信号は、前記全画面情報によって構成された信号を含むことを特徴とするディジタル信号記録再生システム。

【請求項13】 第1の信号と第2の信号からなるディジタル映像信号を受信及び復調する受信手段と、受信した前記第1の信号と前記第2の信号を第3の信号に合成する合成手段と、を含む受信装置、及び、前記第1の信号と前記第2の信号を分離して記録する記録装置をもつディジタル信号記録システムであって、

前記受信装置で合成された前記第3の信号を入力する入力手段と、前記入力手段で入力した前記第3の信号を前記第1の信号と前記第2の信号に分離する分離手段と、前記分離手段で分離した前記第1の信号と前記第2の信号を記録媒体上に記録する記録手段と、を設けたことを特徴とするディジタル信号記録システム。

【請求項14】 第1の信号と第2の信号からなるディ

ジタル映像信号を再生するディジタル信号再生システム であって、

前記第1の信号と前記第2の信号を再生する再生手段 と、前記再生手段で再生された前記第1の信号と前記第 2の信号を第3の信号に合成する合成手段と、前記合成 手段で合成された前記第3の信号を出力する出力手段 と、を設けたことを特徴とするディジタル信号再生システム。

【請求項15】 第1の信号と第2の信号からなるディ ジタル映像信号を受信及び復調する受信手段と、受信し た前記第1の信号と前記第2の信号を第3の信号に合成 する合成手段と、を含む受信装置、及び、前記第1の信 号と前記第2の信号を分離して記録再生する記録再生装 置をもつディジタル信号記録再生システムであって、 前記受信装置で合成された前記第3の信号を入力する入 カ手段と、前記入力手段で入力した前記第3の信号を前 記第1の信号と前記第2の信号に分離する分離手段と、 前記分離手段で分離した前記第1の信号と前記第2の信 号を記録媒体上に記録する記録手段と、前記記録媒体に 記録された前記第1の信号と前記第2の信号を再生する 再生手段と、前記再生手段で再生された前記第1の信号 と前記第2の信号を第4の信号に合成する合成手段と、 前記合成手段で合成された前記第4の信号を出力する出 力手段と、を設けたことを特徴とするディジタル信号記 録再生システム。

【請求項16】 第1の信号と第2の信号からなるディジタル映像信号を記録する記録部をもつディジタル信号 記録システムであって、

前記ディジタル信号を受信及び復調する受信手段と、前 記受信手段で受信した前記第1の信号と前記受信手段で 受信した前記第2の信号との同期化を行う同期化手段 と、前記同期化手段により同期化された前記第1の信号 及び前記第2の信号を記録媒体上に記録する記録手段 と、を設けたことを特徴とするディジタル信号記録システム。

### 【発明の詳細な説明】

#### [0001]

【産業上の利用分野】本発明は、ディジタル信号記録システム及びディジタル信号再生システム及びディジタル信号再生システム及びディジタル信号記録再生システムに係り、特に圧縮された2種類のディジタル映像信号を記録再生するシステムに関するものである。

#### [0002]

【従来の技術】高精細画面のテレビとして、テレビジョン学会誌,46巻3号(1992年)第276頁~283頁の「欧米における次世代テレビ方式の動向」中のADTV(Advanced Digital Television)方式などに記載のように、ディジタル映像信号を圧縮して伝送するディジタルテレビ放送方式が考えられている。

【0003】図2はディジタル映像信号の圧縮方法を示

したものであり、同図において、21及び22はテレビ 画面の1フレームを表している。映像信号の圧縮は、斜 線で示すような例えば9フレームおきのフレームは、フ レーム内の全画像情報の圧縮を行い、その他のフレーム は前または後のフレームのデータよりの予測を用いて差 分情報のみの圧縮を行うことにより、伝送量を低減させ ている。以下の説明では、前者をイントラフレーム、後 者をインターフレームと呼び、パケットを構成して伝送 される。

【0004】このようなディジタル放送によって送られてきた映像信号を記録する場合には、圧縮されているディジタル映像信号をそのまま記録すれば、記録容量が少なく、効率の良い記録を行うことができる。

#### [0005]

【発明が解決しようとする課題】しかし、上記したようなイントラフレームとインターフレームの2種類の圧縮ディジタル映像信号を記録する場合には、受信装置と記録再生装置との接続信号線の数が増加し、システムが複雑になる問題が生じる。

【0006】また、イントラフレームとインターフレームでは、伝送レートが異なり、それぞれ別の受信、復調処理が行われるため、両者の信号間には一般にジッターが含まれており、完全な同期関係が保たれない場合がある。そこで、このような2種類の圧縮されたディジタル信号を記録する際には、両者の非同期性を吸収しないと、記録信号に過不足が生じる危険性がある。

【0007】本発明の目的は、完全な同期関係には無い 2種類のディジタル信号からなる圧縮画像信号を、過不 足なく記録再生でき、かつ、受信装置と記録再生装置と の間の接続信号線の数を低減できるディジタル信号記録 再生システムを提供することにある。

#### [0008]

【課題を解決するための手段】本発明によるディジタル信号記録再生システムは、上記目的を達成するため、受信装置には、受信及び復調されたイントラフレームを含む第1の信号とこれとは異なる第2の信号をビットシリアルで出力する出力手段を設け、記録再生装置には、第1の信号を入力する第1の入力手段と、第1の入力手段で入力した第1の信号を記憶する第1の記憶手段と、第2の信号を入力する第2の入力手段と、第2の入力手段で入力した第2の信号を記憶する第2の記憶手段と、第1の記憶手段に記憶された第1の記憶信号と第2の記憶手段に記憶された第2の記憶信号とを同期化された速度で読み出して記録媒体上に記録する記録手段と、を設けた構成とされる。

【0009】また、記録再生装置には、バッファ手段を、第1の信号または第2の信号、あるいは第1の信号と第2の信号の両方のために設けるようにしてもよい。 【0010】また、受信装置で第1の信号と第2の信号

から第3の信号を合成して出力し、記録再生装置で第3

の信号から第1の信号と第2の信号に分離して記録する ようにしてもよい。

#### [0011]

【作用】受信装置で復調後の信号を入出力すれば、機能的に分離したポイントから信号を取り出せるので、システムが単純化できる。また、ビットシリアル転送とすることで、接続信号線の本数を減少できる。

【0012】また、第1の信号と第2の信号をそれぞれ別の記憶回路で独立に記憶することにより、第1の信号と第2の信号の間にジッターが存在し、完全な同期関係になくてもそれぞれの記憶回路に過不足無く記憶することができる。さらに、記録媒体上に第1の信号及び第2の信号を記録する際に、それぞれの記憶手段に信号を一定量記憶してから、時間軸圧縮した同一の周波数で読み出して記録することにより、それぞれの記憶手段に記憶された信号を全て過不足無く記録媒体に記録することが可能となる。また、非同期吸収用のバッファを設けた場合も、全く同じ理由により、同様の効果が得られる。

【0013】また、第1の信号と第2の信号を合成して 第3の信号を生成して伝送することにより、さらに接続 信号線の数を減少できる。

#### [0014]

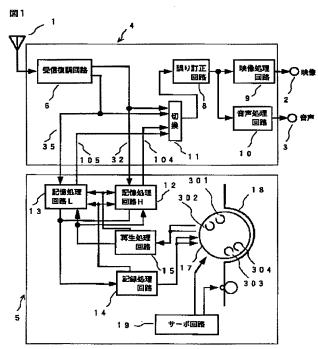

【実施例】以下、本発明の詳細を図示した実施例によって説明する。図1は、本発明の1実施例に係るディジタル信号記録再生システムの構成を示すブロック図であり、同図において、4は外部から伝送されてきたディジタル映像信号を受信する受信装置、5は受信装置4に接続された記録再生装置で、受信装置4から伝送されてきたディジタル映像信号を磁気テープ等の記録媒体に記録し、また、記録媒体に記録された信号を再生する。

【0015】上記受信装置4において、1はアンテナ、6は信号を受信し、受信したディジタル信号を復調する受信復調回路、8は伝送時に発生した誤りを訂正する誤り訂正回路、9は圧縮されている映像信号を伸張する映像処理回路、10は映像信号と共に伝送されてきた音声信号を処理する音声処理回路、11は切換回路、2は映像信号の出力端子、3は音声信号の出力端子である。

【0016】また、上記記録再生装置5において、12及び13は、受信装置4と記録再生装置5とのディジタル信号の入出力を行う記憶処理回路H及び記憶処理回路L、14は入力されたディジタル映像信号より記録信号を生成する記録処理回路、15は再生信号よりディジタル信号を復調する再生処理回路、17は回転シリンダ、18は磁気テープ、19は、磁気テープ18の送り速度等の制御や回転シリンダ17の回転数等の制御を行うサーボ回路である。

【0017】301~304は上記回転シリンダ17に 搭載された磁気ヘッドであり、本実施例においては、従 来からのVHS規格のVTRにおける映像用の磁気ヘッド(ヘッドA)301及び303に、同様の映像用の磁 気ヘッド(ヘッドB)302及び304を追加した構成となっている。ここでは各ヘッドに、従来のVHS規格のVTRにおける3倍モードのトラック幅である、19 $\mu$ mのトラック幅で記録するヘッドを用いる。なお、音声信号は、記憶処理回路H12及び記憶処理回路L13からの出力信号中に含まれているため、映像信号と音声信号を別々に記録する必要が無いので、磁気ヘッド(ヘッドB)302、304は、従来のVHS規格のVTRにおける音声用の磁気ヘッドを、映像用のヘッドに付け替たもので構成しても良い。

【0018】上記した構成において、受信装置4では、通常の受信時には、切換回路11は受信復調回路6の出力を選択しており、出力端子2及び3より映像信号及び音声信号が出力され、同時に受信復調回路6から記録再生装置5に圧縮されたままのディジタル映像信号が出力される。また、記録した信号を再生する時には、受信装置4の切換回路11は、記憶処理回路H12及び記憶処理回路L13の出力を選択しており、記録再生装置5で再生された信号を誤り訂正回路8に入力する。誤り訂正回路8では、入力されたディジタル映像信号に付加されている誤り訂正符号により誤り訂正を行う。その後に、映像処理回路9及び音声処理回路10によって伸張等の処理を行い、出力端子2及び3より出力する。

【0019】誤り訂正前の信号を記録再生装置5で記録しこれを再生することにより、受信装置4の誤り訂正回路8において、伝送時に発生した誤りを訂正すると同時に、記録再生装置5で発生した訂正不能な誤りについても、誤りの検出及び訂正を行うことができる。なお、記録再生装置5で発生した訂正不能な誤りについては、再生信号と共に誤りを示すフラグを記録再生装置5より受け取るようにしてもよい。

【0020】記録再生装置5では、記録時には、記録処理回路14において受信装置4より入力されたディジタル映像信号に、記録用の誤り訂正符号や同期信号等を付加して記録信号を生成し、回転シリンダ17により磁気テープ18に記録する。再生時には、回転シリンダ17によって再生された信号が再生処理回路15に入力され、記録再生時に発生した誤りの訂正等を行い、ディジタル信号の復調を行う。そして、受信回路4に出力する。

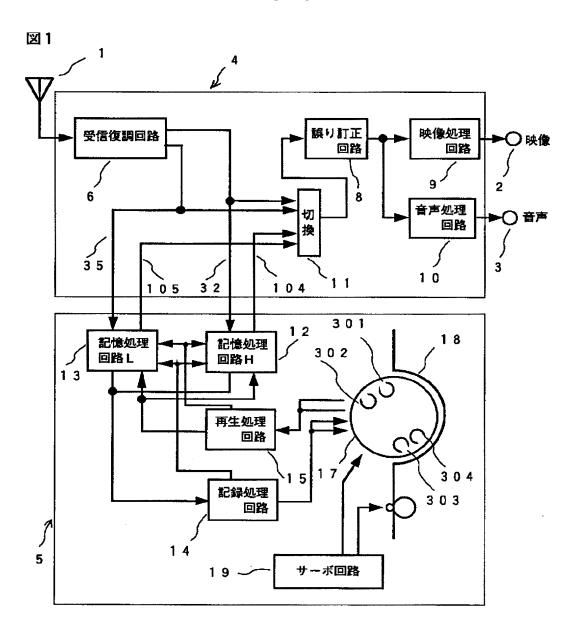

【0021】図3は、受信復調回路6より記録再生装置5に出力する信号の1例を示したものである。受信復調回路6では、ディジタル映像信号を優先度の高いものと低いものに分離して出力する。ここで、優先度の高いデータをHデータ32、優先度の低いデータをLデータ35と呼ぶ。Hデータ32とLデータ35の伝送レートは、それぞれ4.32Mbps,17.28Mbpsであり、データ量の比率は1:4としている。それぞれのデータは、ビットシリアルで転送され、それぞれに対して同期しているHビットクロック34,Lビットクロック

ク37とともに送られて来る。

【0022】本実施例のシステムのように、2種類の信号を記録再生する場合、接続信号線の数が2倍になる問題が生じるが、上記したビットシリアルの接続仕様とすることで、パラレル接続の場合と比べて、接続信号線の数を減少させることができる。また、受信装置4側も、記録再生装置5との入出力を行う個所が、機能的に分離したところであるため、受信装置4側の設計も容易に行うことができる。

【0023】記録再生装置5の記憶処理回路H12は、Hデータ入力32とHビットクロック34を入力して、1ワード=8ビットごとに区切ってH記憶データ33として記録処理を行う。また、記憶処理回路L13は、L入力データ35とLビットクロック37を入力して、同様に1ワード=8ビットごとに区切ってL記憶データ36として記録処理を行う。

【0024】ここで、Hデータ32は、例えば、そのフレームのデータのみで伸張を行うことのできるイントラフレームデータや重要度の高い制御信号により構成し、Lデータ35は、例えば、前または後のフレームのデータも用いて伸張を行うインターフレームデータや音声データにより構成する。尚、優先度の高いものと低いものの分離は、記録再生装置5で行ってもよい。

【0025】図4に、記録タイミングを示す。41は、磁気ヘッド(Aヘッド)301及び303の切換タイミングを示す信号であり、例えば、信号41が「H」の時磁気ヘッド301が記録状態に、信号41が「L」の時磁気ヘッド303が記録状態にあることを示し、回転シリンダ17の回転と同期するものとなっている。ここでは、H記憶データ33の148ワード×60の入力区間を、回転シリンダ17の半回転時間としている。

【0026】図4において、44は磁気ヘッド(Aヘッド)301及び303による磁気テープ18上への記録タイミング、45は磁気ヘッド(Bヘッド)302及び304による磁気テープ18上への記録タイミングを、それぞれ示す。なおここでは、Bヘッド302及び304がAヘッド301及び303に対して、60°ずれた位置に取り付けられているものとしている。磁気テープ18へは、後述する156ワードからなるブロックを単位として、60ブロック×3個の記録エリアに分割して記録する。

【0027】図4に示すように、各トラックとも最初の2個の領域には、Lデータを記録し、Aヘッド301及び303により3個目の領域にHデータを記録する。同図中、47で示した部分は、回転シリンダ17の回転ジッターを吸収するためのマージン用アンブル部である。また、Bヘッド302及び304における3個目の領域48は、未使用としているが、ここにHデータを多重記録しても良い。

【0028】図5は、磁気テープ18に記録されるブロ

ックの構成図である。同図において、201は1ワードからなる同期信号、202はブロックの位置を示すブロック番号等からなる3ワードのID信号、203は148ワードからなるHデータまたはLデータ、204はデータ203の誤り検出訂正を行うための4ワードからなるC1パリティである。各ブロックは156ワードで構成される。なお、記録時の変調方式として8-10変調を用いると、1ワードは10ビットから構成される。

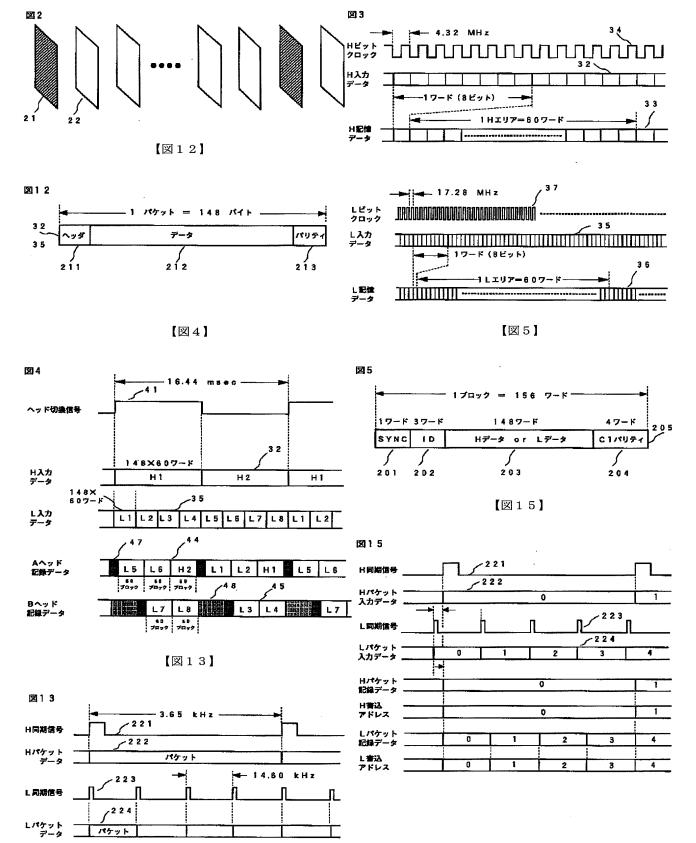

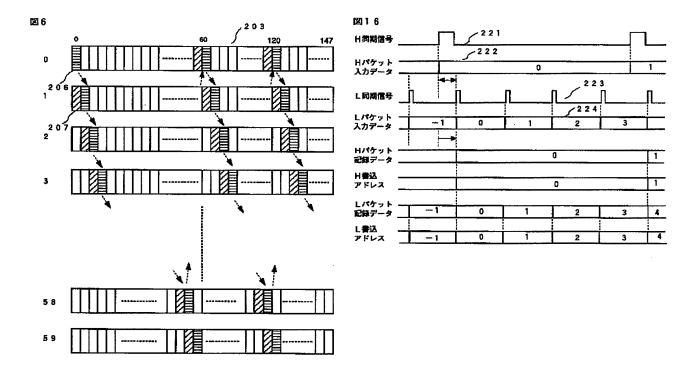

【0029】図6は、図4に示す60ブロックから成る 各領域における、入力データと記録データとのインタリ ーブの関係を示したものである。同図中の各行(各段) は、それぞれ図5におけるデータ(HデータまたはLデ ータ)203を示しており、各段の1つ1つのますが1 ワードを表わしている。

【0030】図6において、横線を施した各ます206の全体が、1個の各入力データに相当し、同図に示すように、1個の各データを60ブロックの全てに分散させて記録する。こうすることにより、再生時に、テープ上のドロップアウト等でバーストエラーが発生しても、そのエラーを時間軸上で離れている多数のデータに分散でき、受信装置4の誤り訂正回路8で訂正することが可能となる。なお、この次の1個の各データは、斜線を施した各ます207の全体で示されている。

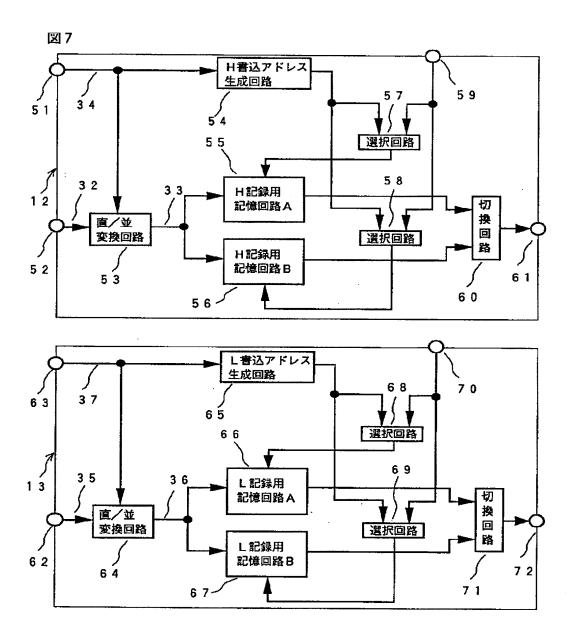

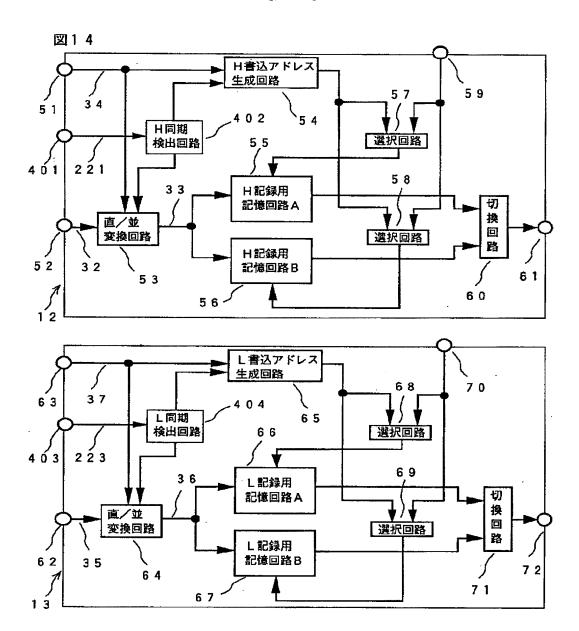

【0031】図7は、前記記憶処理回路H12及び記憶処理回路L13の記録に関する部分の構成図である。同図の記憶処理回路H12側において、51はHビットクロック入力端子、52はHデータ入力端子、53はシリアルデータを8ビットのパラレルデータに変換する直/並変換回路、55,56は直/並変換回路53の出力を一時記憶する記憶回路(H記録用記録回路A,B)、54は、記憶回路55及び56の書込アドレスを生成する日書込アドレス生成回路、57及び58は記憶回路55,56のアドレスを切り換える選択回路、59は、前記録処理回路14より記憶回路55,56の読み出しアドレスを入力するH読み出しアドレス入力端子、60は記録するデータとして、記憶回路55か56かを選択する切換回路、61は記録処理回路14へデータを出力するH記録データ出力端子である。

【0032】また、図7の記憶処理回路L13側において、63はLビットクロック入力端子、62はLデータ入力端子、64はシリアルデータを8ビットのパラレルデータに変換する直/並変換回路、66,67は直/並変換回路64の出力を一時記憶する記憶回路(L記録用記録回路A,B)、65は、記憶回路66及び67の書込アドレスを生成するL書込アドレス生成回路、68及び69は記憶回路66,67のアドレスを切り換える選択回路、70は、前記記録処理回路14より記憶回路66,67の読み出しアドレス入力するL読み出しアドレス入力端子、71は記録するデータとして、記憶回路66か67かを選択する切換回路、72は記録処理回路

14ヘデータを出力するL記録データ出力端子である。 【0033】以下、図7を用いて、記録時の動作について説明する。Hデータ入力端子52及びLデータ入力端子62から入力されたH入力データ32及びL入力データ35は、それぞれ直/並変換回路53,64により図3に示したように8ビット(1ワード)ごとに区切られ、H記憶データ33及びL記憶データ36に変換される。H,L記憶データ33、36は、Hビットクロック34及びLビットクロック37により動作する書込アドレス生成回路54及び65に従って、H記録用記憶回路55,56及びL記録用記憶回路66,67に記憶される。

【0034】この際、選択回路57,58及び選択回路68,69の働きにより、記憶処理回路H12及び記憶処理回路L13の双方において、どちらかの記憶回路AもしくはBが選択されて記憶される。例えば、図4に示したヘッド切換信号41が「H」の時、H記録用記憶回路A55及びL記録用記憶回路A66に、「L」の時、H記録用記憶回路B56及びL記録用記憶回路B67に、それぞれ記憶データが記憶される。

【0035】またこれと同時に、磁気テープ18に記録するため、記憶回路55,56及び66,67より、記録処理回路14にデータを読み出す必要がある。この時、選択回路57,58及び選択回路68,69、切換回路60及び71の働きにより、記憶動作の行われていない方の記憶回路を選択して、データの読み出しを行う。即ち、ヘッド切換信号41が「H」の時、H記録用記憶回路B56及びL記録用記憶回路B67よりデータの読み出しが行われ、また、ヘッド切換信号41が

「L」の時、H記録用記憶回路A55及びL記録用記憶回路A66よりデータの読み出しが行われる。

【0036】このデータの読み出しは、H読み出しアドレス入力端子59及びL読み出しアドレス入力端子70より入力される読み出しアドレスに従って、ビットクロック34及び37とは無関係の速度で行われる。記録に要する時間は、図4の44,45に示したように、入力に要する時間より時間軸圧縮されているため、記憶回路55,56及び66,67に書き込む速度より、読み出す速度の方が早くなる。図4に示した前記マージンアンブル部47は、この記憶回路55,56及び66,67の書き込み、読み出しの切換タイミングのマージンの役割も果たしている。

【0037】図7に示し上述したように、Hデータ、Lデータに対して独立の記憶回路を設け、Hデータ入力、Lデータ入力とを互いに独立させて記憶回路へ書き込むことにより、HデータとLデータとの間にジッターが存在して、完全な同期関係に無い場合でも、両データとも過不足無く記憶回路に記憶することができる。また、別の期間でHデータとLデータの両方を書き込む速度より速い速度で読み出して記録媒体に記録することにより、

記憶回路に記憶された全データを過不足無く記録することが可能となる。

【0038】これにより、ジッターを含み、完全な同期 関係に無い2種類の信号を、ジッター等の影響を受けず に同期化することが可能となり、同時に完全に記録する ことができる。

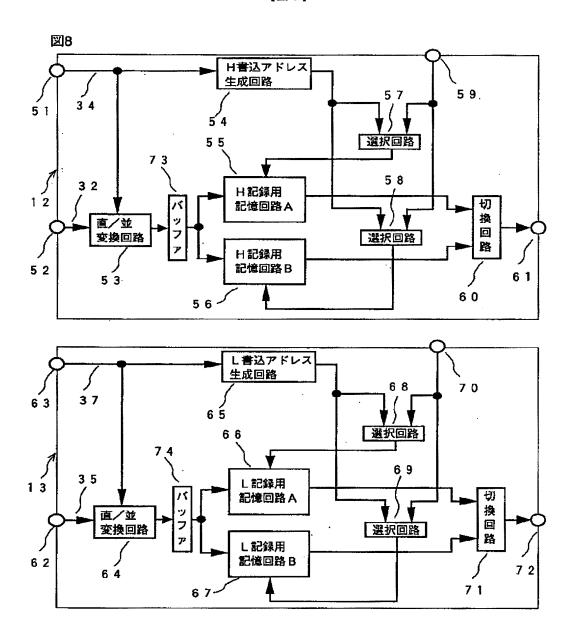

【0039】なお図7に示した例では、2種類の信号の非同期吸収を、記憶回路55,56及び66,67の読み出し時に行っていたが、図8に示すように、記憶回路55,56及び66,67の前にバッファを設けても全く同様の効果を得ることができる。図8において、73,74は非同期吸収用のバッファであり、例えば、数段のシフトレジスタや小容量のメモリ等からなる。

【0040】図8に示した構成においては、Hビットクロック34、Lビットクロック37にそれぞれ従って、直/並変換回路53及び64の出力を、それぞれバッファ73、74に蓄え、両バッファを同期した速度でそれぞれ記憶回路55、56及び記憶回路66、67に出力することにより、同期化を行える。

【0041】なおまた、図8ではバッファ回路を2個用いていたが、1個のバッファ回路のみでも良い。例えば、バッファ74のみを備え、バッファ73を持たない場合、バッファ74の出力速度を、Hビットクロック34と同期させることにより、両者を同期化することが可能となる。

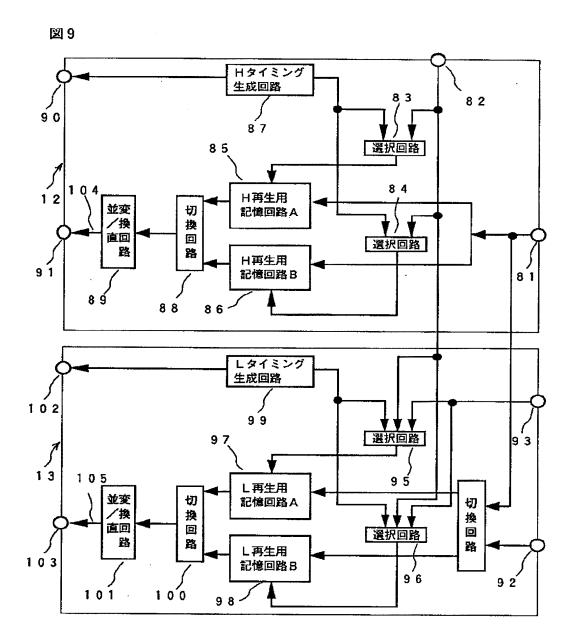

【0042】図9は前記記憶処理回路H12及び記憶処 理回路L13の再生に関する部分の構成図である。同図 の記憶処理回路H12側において、81は、前記再生処 理回路15より再生データを入力するA再生データ入力 端子、85,86は再生データを一時記憶する記憶回路 (H再生用記憶回路A, B)、82は、再生処理回路1 5より記憶回路85,86の書込アドレスを入力するA 書込アドレス入力端子、83,84は、記憶回路85, 86のアドレスを切り換える選択回路、87は、記憶回 路85,86からデータを読み出して、外部へ出力する ためのタイミングを生成するHタイミング生成回路、8 8は、出力するデータとして記憶回路85の出力か記憶 回路86の出力かを選択する切換回路、89はパラレル データをシリアルデータに変換する並/直変換回路、9 0はHビットクロック出力端子、91はHデータ出力端 子である。

【0043】また、図9の記憶処理回路L13側において、92は、前記再生処理回路15より再生データを入力するB再生データ入力端子、97,98は再生データを一時記憶する記憶回路(L再生用記憶回路A,B)、93は、再生処理回路15より記憶回路97,98の書込アドレスを入力するB書込アドレス入力端子、95,96は、記憶回路97,98のアドレスを切り換える選択回路、99は、記憶回路97,98からデータを読み出して、外部へ出力するためのタイミングを生成するL

タイミング生成回路、100は、出力するデータとして記憶回路97の出力か記憶回路98の出力かを選択する切換回路、101はパラレルデータをシリアルデータに変換する並/直変換回路、102はLビットクロック出力端子、103はLデータ出力端子である。

【0044】図8を用いて、再生時の動作を説明する。 Hタイミング生成回路87及びLタイミング生成回路9 9は、それぞれH入力データ32(4.32MHz)及びL入力データ35(17.28MHz)の伝送レートで出力されるような周期のクロックで動作し、それぞれの出力データと同期したビットクロックをHビットクロック出力端子90及びLビットクロック出力端子102より出力する。なお、この2本のクロックの基準となる信号は、受信装置4から入力しても良い。

【0045】再生時も、記録時と同様に、選択回路83,84及び選択回路95,96と、切換回路88,100との働きにより、記憶回路85,86及び97,98の書き込みタイミング、並びに読み出しタイミングを分離している。例えば、ヘッド切換信号41が「H」の時、H再生用記憶回路A85及びL再生用記憶回路A97に再生データの書き込みを行い、同時に、H再生用記憶回路B86及びL再生用記憶回路B98から出力データの読み出しを行う。また、ヘッド切換信号41が

「L」の時、H再生用記憶回路B86及びL再生用記憶回路B98に再生データの書き込みを行い、同時に、H 再生用記憶回路A85及びL再生用記憶回路A97から 出力データの読み出しを行う。

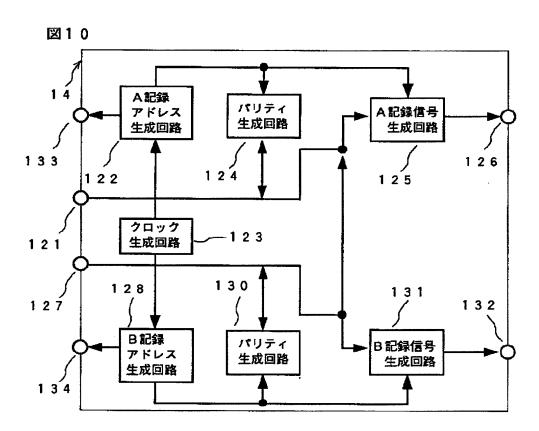

【0046】図10は、前記記録処理回路14の構成図である。同図において、121はH記憶データ入力端子、127はL記憶データ入力端子、133は、前記記憶処理回路H12へ記憶回路55,56の読み出しアドレスを出力するAアドレス出力端子、134は、前記記憶処理回路H12及び前記記憶処理回路L13へ記憶回路66,67の読み出しアドレスを出力するBアドレス出力端子、126は磁気ヘッド301及び303へ記録データを出力するA記録データ出力端子、132は磁気へッド302及び304へ記録データを出力するB記録データ出力端子である。

【0047】図10の記録処理回路14では、図6に示したインタリーブに従って、記憶処理回路H12及び記憶処理回路L13から読み出されたデータを図5に示すデータ203とし、これにパリティ生成回路124, 130によりC1パリティ204を付加し、その後、記録信号生成回路(A及びB記録信号生成回路)125, 131により、同期信号201, ID信号202を付加して、各ヘッドへ記録データの出力を行う。

【0048】図10に示すように、前記した各記憶回路55,56及び66,67の読み出しアドレスを生成するA記録アドレス生成回路122及びB記録アドレス生成回路128は、記憶処理回路H12及び記憶処理回路

L13とは独立に動作するクロック生成回路123に従って動作するものであり、H入力データ32とL入力データ35間のジッターの影響を受けずに、磁気テープ18に記録することができる。

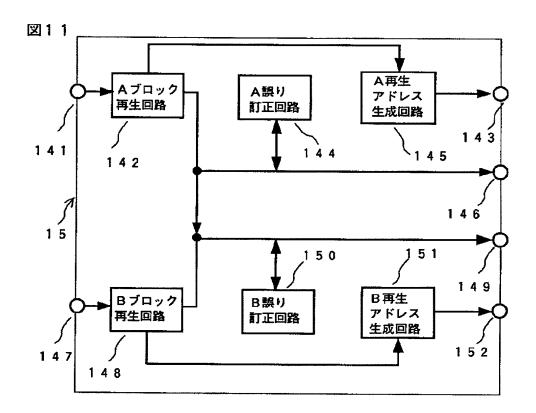

【0049】図11は、前記再生処理回路15の構成図である。同図において、141は、磁気ヘッド301及び303からの再生信号を入力するA再生データ入力端子、147は、磁気ヘッド302及び304からの再生信号を入力するB再生データ入力端子、146は、再生データを記憶処理回路H12及び記憶処理回路L13に出力するA再生データ出力端子、149は、再生データを記憶処理回路L13に出力するB再生データ出力端子、143は、記憶回路55,56及び66,67の書込アドレスを出力するA書込アドレス出力端子、152は、記憶回路66,67の書込アドレス出力端子である。なお、A再生アドレス生成回路145及びB再生アドレス生成回路151は、再生されるデータから抽出される再生クロック(図中には明記されていない)により動作する。

【0050】図11の再生処理回路15において、前記各磁気ヘッド301~304によって再生された信号は、Aブロック再生回路142及びBブロック再生回路148により、同期信号201, ID信号202の検出を行い、A誤り訂正回路144及びB誤り訂正回路150により、C1パリティ204を用いた誤り検出と訂正を行う。

【0051】以上では、H入力データ, L入力データには、特別なパケット構造が無く、ただ単にビットシリアルでデータを転送する場合について述べてきたが、入力データがパケット構造を持つ場合も考えられる。

【0052】例えば、図12に示すように、ヘッダ211と、データ212と、前記受信機4の誤り訂正回路8で行う誤り訂正用のパリティ213との148バイト(1バイト=8ビット)で、1パケットを構成して転送される場合がある。このとき、図13に示すように、各パケットの先頭を示すH同期信号221, L同期信号223が、Hパケットデータ222, Lパケットデータ224にそれぞれ付加されて転送される。従って、記録再生装置5では、再生時にこのパケット構造を再現して再生する必要がある。

【0053】図14は、この場合に対応するための前記記憶処理回路H12及び記憶処理回路L13の記録に関する部分の構成図である。同図に示した構成は、前記図7の記憶処理回路H12に、H同期信号入力端子401とH同期検出回路402とを追加し、前記図7の記憶処理回路L13に、L同期信号入力端子403とL同期検出回路404とを追加したものであり、それぞれH同期信号221及びL同期信号223により、パケットの先頭を検出し、直/並変換回路53,64を制御し、記憶回路55,56及び66,67の書込アドレスを制御す

る。これにより、各パケットの構成を維持したまま、H パケットデータ222の先頭とLパケットデータ224 の先頭を同期化させて記録することができる。

【0054】図15,図16に、Hパケットデータ22 2とLパケットデータ224の同期化の例を示す。一般 にH同期信号221とL同期信号223は非同期に入力 され、両者の先頭データの入力タイミングは一致しな い。そこで、H同期信号の入力タイミングに最も近いL 同期信号に示されるパケット先頭データの記憶回路5 5,56への記憶アドレスを制御する。

【0055】図15に示すようなタイミングで各同期信号221,223が入力される場合は、Lパケットデータを遅らせて記憶することになり、図16の場合は、逆にHパケットデータを遅らせて記憶することになる。

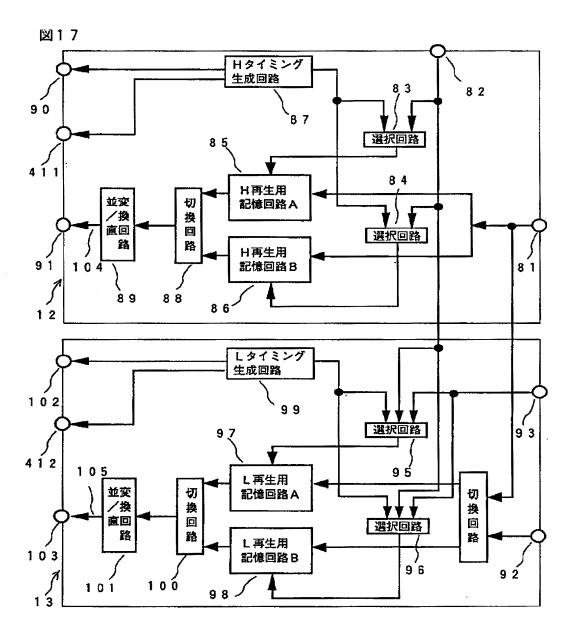

【0056】また、図17は、同様にパケット構造を持 つデータを再生する場合の記憶処理回路H12及び記憶 処理回路L13の再生に関する部分の構成図である。同 図に示した構成は、前記図9の記憶処理回路H12及び 記憶処理回路L13に、各タイミング生成回路87,9 9よりの同期信号を出力するH同期信号出力端子411 及びL同期信号出力端子412をそれぞれ追加したもの である。前記したように記録時に、各同期信号(H同期 信号、L同期信号)221、223に応じて、記憶回路 55,56及び66,67の書込アドレスを制御してい るので、Hデータ, Lデータのパケットの先頭は、記憶 回路85,86及び97,98の読み出しアドレスより 判別することができるため、H, L書込アドレス生成回 路により各同期信号を生成することができる。このH同 期信号, L同期信号を出力することにより、受信装置4 側でも、記録時と同一のパケット構成を再現することが 可能となる。

【0057】尚、図7、図9あるいは図14、図17では、記録用の記憶回路55、56及び66、67と、再生用の記憶回路85、86及び97、98を別の回路として扱っているが、記録用の記憶回路と再生用の記憶回路は、同一の回路でも良い。その場合、例えば、記憶回路55と85、56と86、66と97、67と98を同一の記憶回路として使用できる。

【0058】また、図6で説明したインターリーブは、行なわくても差し支えない。また、記憶再生装置5における誤り訂正符号として、C1パリティ204のみとしているが、この他に各ブロック間にわたる訂正符号としてC2パリティを導入しても良い。

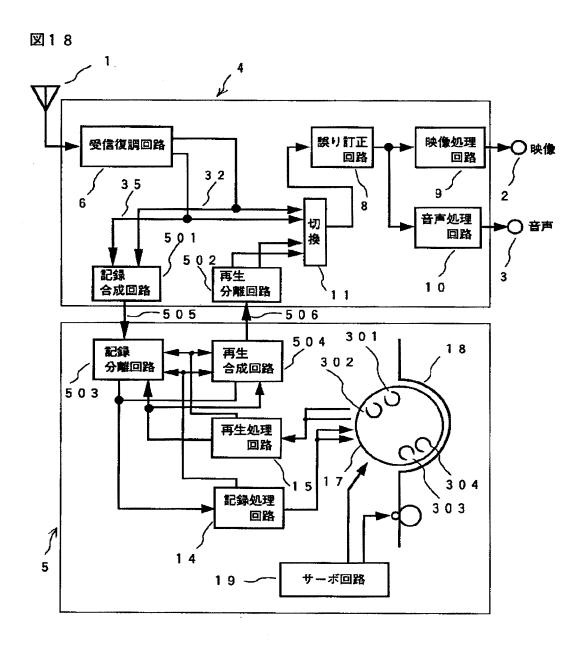

【0059】また、Hデータ32とLデータ35は1本の信号線に合成して転送するようにしてもよい。この場合、データの転送レートは増加するが、接続信号線の数をさらに減少させることができる。図18に、この場合の受信装置4と記録再生装置5の構成を示す。同図において、501は、H入力データ32とL入力データ35から記録合成データ505を生成する記録合成回路、5

03は、記録合成データ505からHデータ32とLデータ35に分離する記録分離回路である。また、504は、再生されたHデータとLデータから再生合成データ506を生成する再生合成回路、502は、再生合成データ506からHデータとLデータに分離する再生分離回路である。ここで、記録合成回路501に、Hデータ32とLデータ35のそれぞれにバッファ回路等を設けることにより、図8の回路動作の説明で述べたものと同様の理由により、2種類の信号の非同期性の問題を避けることができる。なお、ここでの記録合成データ505及び再生合成データ506の伝送レートは、例えば21.6Mbps (4.32Mbps+17.28Mbp)

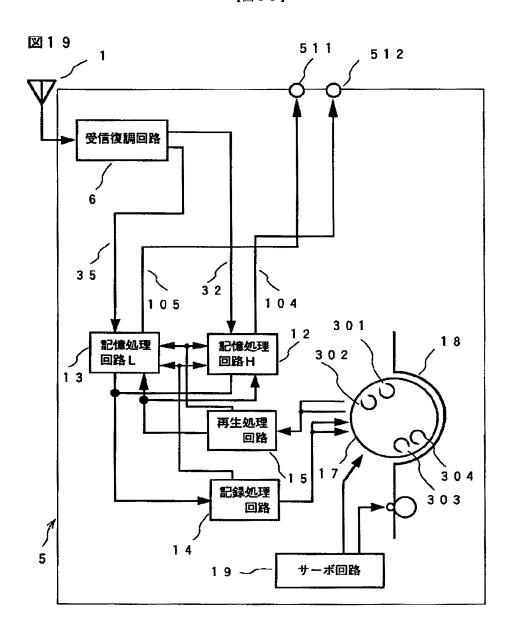

【0060】尚、これまでに説明した記録再生装置5は、必ず受信装置4からの信号を入力しなければ記録動作が行えない。そこで、記録再生装置5単独でも記録動作が行えるように、受信装置の機能を記録再生装置5に備えることも考えられる。その際、受信装置4の回路を全て備えると、回路規模が極めて増大してしまうので、一部の回路のみを備えれば良い。図19は、この場合の記録再生装置5の構成を示したものであり、アンテナ1及び受信復調回路6を備えている。これにより、最小の回路構成で、受信装置4が存在しなくても、記録再生装置5単独で記録動作を行うことが可能となる。

【0061】尚また、以上の説明では、信号の種類として2種類の場合についてのみ述べてきたが、3種類以上の信号を記録再生する場合でも、本発明を用いることにより、全く同様の効果を得ることができる。この場合、記憶回路を信号の種類に比例した個数だけ用いるか、バッファ回路を信号数が増加した分だけ追加すれば良いことになる。

### [0062]

s) となる。

【発明の効果】以上のように本発明によれば、2種類のディジタル信号からなる圧縮画像信号を記録再生するシステムにおいて、受信装置と記録再生装置との間を、記録再生各4本(同期信号を用いる場合は6本)ずつの接続で、記録再生することができる。

【0063】また、2種類のディジタル信号に、完全な同期関係が無く、ジッターを含んでいる場合でも、両信号の同期化を行うことが可能であり、過不足無く記録することができる。また、入力される各データが、それぞれパケット構造を持っている場合でも、同様に2種類の信号の同期化を行うことができる。

【0064】さらに、2種類のディジタル信号を1種類の信号に合成して伝送することにより、記録再生各2本(同期信号を用いる場合は3本)ずつの接続で、記録再生することができる。

【0065】さらに、記録再生装置にアンテナと受信復 調回路を設けることにより、記録再生装置単独でも、最 小の回路規模で記録動作を行うことが可能となる。

#### 【図面の簡単な説明】

【図1】本発明の1実施例に係るディジタル信号記録再 生システムの構成を示すブロック図である。

【図2】ディジタル映像信号の圧縮方法の1例を示す説明図である。

【図3】図1の受信装置より記録再生装置に出力する信号のタイミングを示す説明図である。

【図4】本発明の1実施例によるデータの入力タイミング及び記録タイミングを示す説明図である。

【図5】本発明の実施例で用いられるブロックで構成されるデータの1例を示す説明図である。

【図6】本発明の1実施例による入力データと記録データとのインターリーブの関係を示す説明図である。

【図7】図1の記憶処理回路12,13の記録処理系に 関する部分の構成の1例を示すブロック図である。

【図8】図1の記憶処理回路12,13の記録処理系に 関する部分の構成の他の1例を示すブロック図である。

【図9】図1の記憶処理回路12,13の再生処理系に 関する部分の構成の1例を示すブロック図である。

【図10】図1の記録処理回路14の構成を示すブロック図である。

【図11】図1の再生処理回路15の構成を示すブロック図である。

【図12】本発明の実施例で用いられるパケットで構成されるデータの1例を示す説明図である。

【図13】図12の各パケットデータと同期信号のタイミング関係を示す説明図である。

【図14】パケットデータを取り扱うための図1の記憶処理回路12,13の記録処理系に関する部分の構成の1例を示すブロック図である。

【図15】図14の回路動作のタイミングの1例を示す 説明図である。

【図16】図14の回路動作のタイミングの他の1例を示す説明図である。

【図17】パケットデータを取り扱うための図1の記憶 処理回路12,13の再生処理系に関する部分の構成の 1例を示すブロック図である。

【図18】本発明の他の実施例に係るディジタル信号記録再生システムの構成を示すブロック図である。

【図19】本発明のさらに他の実施例に係るディジタル 信号記録再生システムの構成を示すブロック図である。

#### 【符号の説明】

- 4 受信装置

- 5 記録再生装置

- 6 受信復調回路

- 12 記憶処理回路H

- 13 記憶処理回路L

- 14 記録処理回路

- 15 再生処理回路

- 54 H書込アドレス生成回路

- 5 5 H記録用記憶回路A

5 6 H記録用記憶回路B

6 5 L書込アドレス生成回路

6 6 L記録用記憶回路A

6 7 L記録用記憶回路B

7 3, 7 4 バッファ

- 7 3, 7 4 ハッシア8 5 H再生用記憶回路A8 6 H再生用記憶回路B9 7 L再生用記憶回路A

- 97 L再生用記憶回路A 98 L再生用記憶回路B

- 122A記録アドレス生成回路128B記録アドレス生成回路145A再生アドレス生成回路

- 151 B再生アドレス生成回路

- 4 0 2 H同期検出回路 4 0 4 L同期検出回路 5 0 1 記録合成回路

- 502 再生分離回路503 記錄分離回路

- 504 再生合成回路

[図1]

【図6】

【図16】

【図10】

【図7】

【図8】

【図9】

【図11】

【図14】

【図17】

【図18】

【図19】

フロントページの続き

## (72)発明者 斉藤 清一

神奈川県横浜市戸塚区吉田町292番地 株 式会社日立製作所映像メディア研究所内